Diskettenprobleme

von Enrico Grämer

Jeder hat es sicherlich schon erlebt, dass der KC Leseprobleme mit 5,25"-Disketten hat. Besonders häufig ist dies bei PC-formatierten und beschriebenen Disketten der Fall. Allerdings muss es bei der gleichen Diskette nicht zwangsläufig immer derselbe Sektor sein, dieser kann von Zeit zu Zeit variieren. Bei den 3,5"-Disketten tritt das Problem dagegen kaum auf. Nach einigen Tests musste ich feststellen, dass es für diese Erscheinung gleich mehrere Ursachen gibt.

Zum einen war bei mir die Frequenz der PLL, wahrscheinlich aufgrund von Materialalterung der Bauteile, um 50 kHz verstellt. Des weiteren gibt es Designfehler in der Beschaltung der PLL. Weiter erschwerend kommen thermische Probleme hinzu.

Wie man im Schaltplan der D004 erkennen kann, wird die PLL mittels einer Regelschaltung, bestehend aus dem Transistor VT 704 und der Z-Diode VD 702, mit Spannung versorgt.

Das ist nun nicht gerade besonders genau und stabil!

Am Pin 9 der PLL ist ein Spannungsteiler, bestehend aus den Widerständen R 722 und R 721, angeschlossen. R 722 hängt leider nur an den normalen +5 Volt. Auf dieser Leitung kann es zu recht beachtlichen Spannungsschwankungen von ca. 1 Volt (!) kommen. Dadurch ändert sich die Spannung am Teiler und somit die Frequenz der PLL. Besonders kritisch wird es, wenn man eine 2,5"-Platte einbaut. Das gleiche Problem der Spannungsschwankungen besteht beim Widerstand R 703 (Zeitglied) am Monoflop D 705. Dieser wird vom Floppycontroller gesteuert und dient anscheinend als Zerhacker der von der PLL (Pin 2) kommenden Regelspannung. Inwieweit sich die daraus resultierenden Zeitschwankungen des Monoflops auf die Lesegenauigkeit der Diskette auswirken, konnte ich leider nicht herausfinden. Aber ändern kann man die Anschaltung des Widerstands ja sicherheitshalber trotzdem.

Die Widerstände R 722, R 721, R 723 und R 725 am Pin 9 der PLL sind frequenzbestimmend für die Leerlauffrequenz am Pin 3/4 der PLL. Leider sind die damals verwendeten Kohleschichtwiderstände sehr temperaturabhängig und müssen daher gegen entsprechende Widerstandswerte aus Metallfilm ersetzt werden.

Folgende Änderungen sind also notwendig:

- Austausch der Regelschaltung VT 704 und VD 702 gegen einen möglichst genau regelnden Low-Drop-Regler

- Ersetzen der Widerstände R 722, R 721, R 723 und R 725 durch solche aus Metallfilm

- Anschaltung der Widerstände R 722 und R 703 an die geregelte Spannungsversorgung der PLL

- Einstellen der PLL-Frequenz auf 500 kHz.

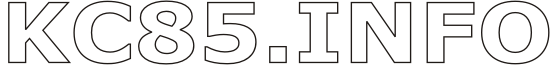

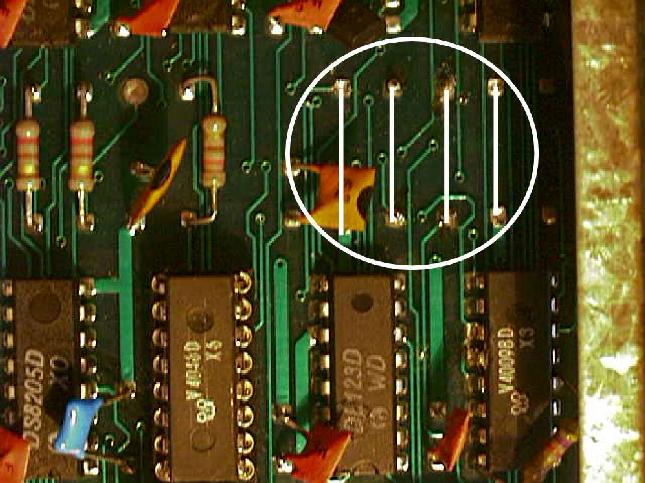

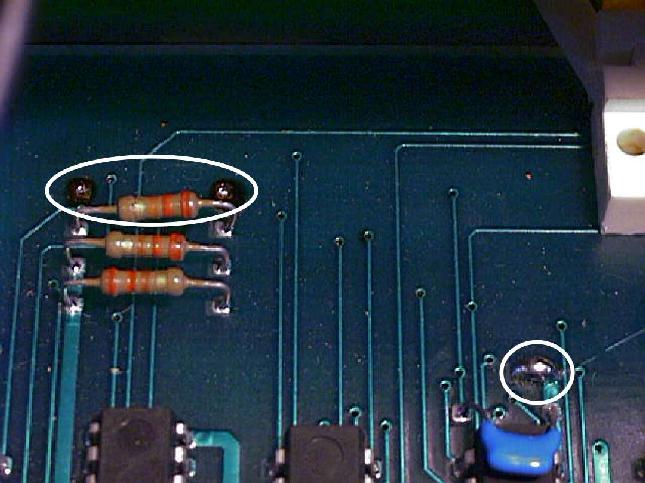

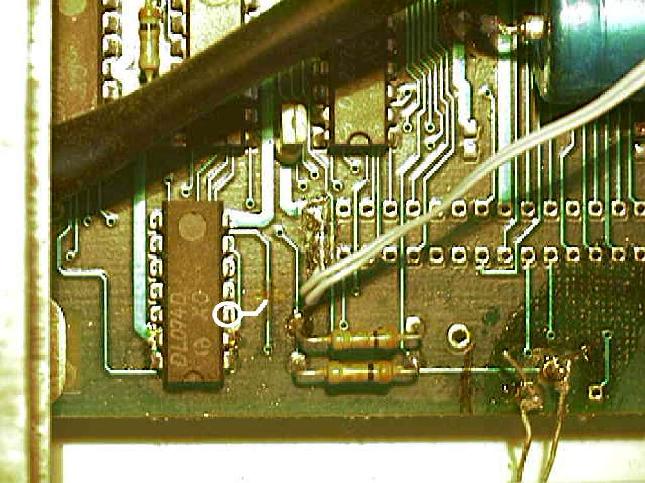

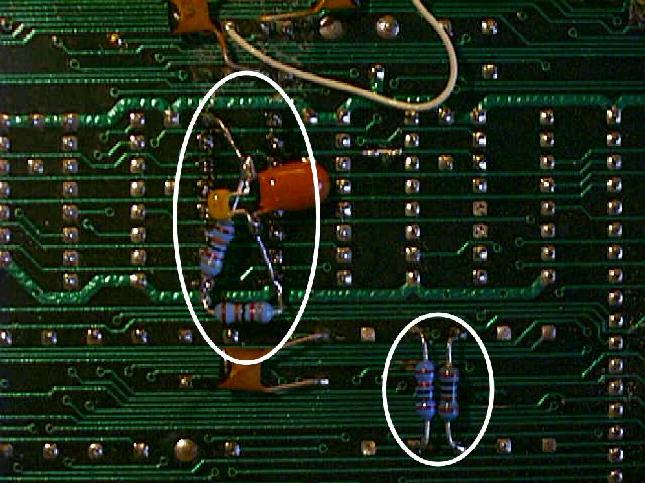

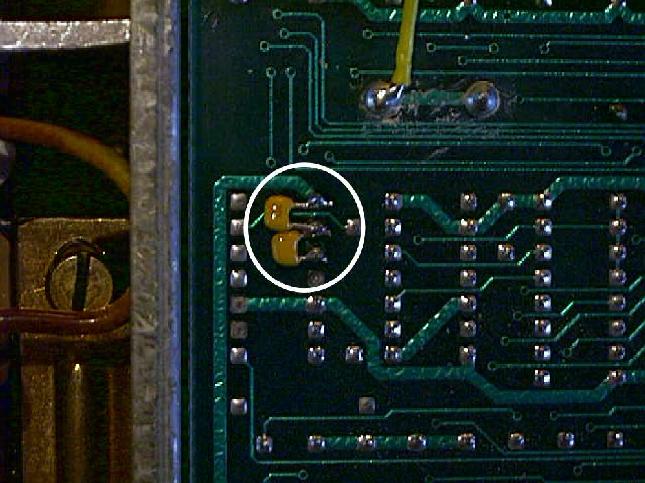

Nachdem man die D004 aufgeschraubt und die Platine für die Module hochgeklappt hat, sieht man das Board der D004. Auf der linken Hälfte der Platine, etwa in der Mitte, befindet sich die PLL V 4046. Rechts oberhalb der PLL sind die Widerstände R 722, R 723, R 725 und R 721 entsprechend Bild 1, die ausgelötet werden. In der hinteren linken Ecke, neben dem Floppystecker, wird der Widerstand R 724 ausgelötet und die Z-Diode VD 702 gebrückt, siehe Bild 2. Bild 3 zeigt zwei Transistoren, die ganz links außen, etwa mittig zu finden sind. Der untere der beiden Transistoren wird durch den Low-Drop-Regler ersetzt. Dabei ist darauf zu achten, dass die gerade Seite des Reglers nach außen zeigt. Auf der Lötseite bekommt der Regler noch je einen 100-nF-Kondensator am Ein- und Ausgang spendiert (Bild 6).

Bild 5 zeigt die PLL von der Unterseite. Über die Stromversorgungsanschlüsse Pin 8 und Pin 16 wird ein 100 nF Kondensator und ein Elko, oder noch besser, ein Tantalkondensator mit ca. 1...4,7 uF geschaltet. Die Widerstände R 722 und R 721 kommen ebenfalls direkt auf die Lötseite, je gegen Pin 9 bzw. Masse oder Pin 16 der PLL geschaltet. Etwas weiter rechts unten sieht man die neu eingelöteten Widerstände R 723 und R 725. Diese 4 Widerstände sind auf jeden Fall auf der Lötseite einzubauen, denn dort fallen die Temperaturschwankungen wesentlich geringer als auf der Bestückungsseite aus.

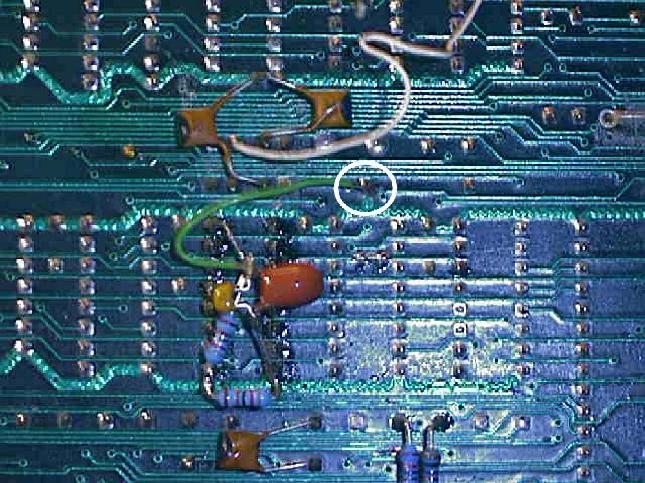

Bild 7 zeigt die Neuverdrahtung von R 703 (Lötseite). Dazu wird der auf dem Bild eingekreiste Anschlusspin des Widerstands von der +5V-Leitung getrennt, und mittels Draht mit Pin 16 der PLL verbunden.

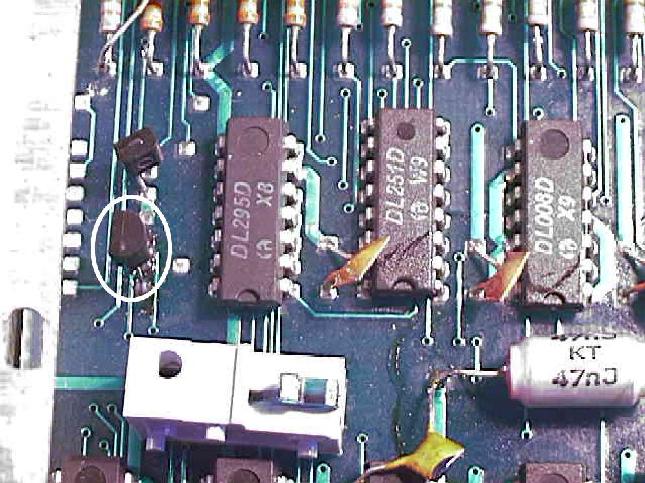

Zum Abschluss muss nur noch die PLL auf 500 kHz eingestellt werden. An Pin 3 des ICs D 601 wird ein Frequenzzähler angeschlossen. Dieser LS 074 befindet sich links vorn in der Ecke, Bild 4. Die 10-Gang-Wendel-Trimmer R 727 und R 728, ganz rechts unten auf der Platine, sind zur Einstellung der 500 kHz gedacht. R 727 ist der Linke, R 728 der Rechte. Die Widerstände dreht man bis zum Anschlag. Dieser ist erreicht, wenn ein Klicken zu hören ist. Ist auch nach spätestens 10 Umdrehungen kein Klicken zu hören, so wurde der Widerstand schon öfters überdreht und ist auszuwechseln, da keine ordnungsgemäße Funktion mehr gewährleistet ist. R 728 wird auf Links- und R 727 auf Rechtsanschlag gestellt. Mit R 727 wird auf etwa 470 kHz grob vorabgeglichen. Anschließend wird mit R 728 auf 500 kHz feineingestellt. Nun gibt man noch etwa eine Viertelumdrehung dazu, dabei sollte sich die Frequenz nicht mehr ändern.

Bauteile:

- R 721, R 722: 820 k, Metallfilm 1 %

- R 723: 20 k, Metallfilm 1 %

- R 725: 1 k, Metallfilm 1 %

- 1 x Low-Drop-Regler, 5 V, 100 mA, z.B. LP 2950

- 3 x 100 nF

- 1 x 1...4,7 uF Elko oder besser Tantal

Bild 1: Zum Umbau des KC-Floppyinterfaces (1).

Bild 2: Zum Umbau des KC-Floppyinterfaces (2).

Bild 3: Zum Umbau des KC-Floppyinterfaces (3).

Bild 4: Zum Umbau des KC-Floppyinterfaces (4).

Bild 5: Zum Umbau des KC-Floppyinterfaces (5).

Bild 6: Zum Umbau des KC-Floppyinterfaces (6).

Bild 7: Zum Umbau des KC-Floppyinterfaces (7).